信息摘要:

PCB阻抗控制的主要挑战材料与工艺波动基板介电常数(Dk)受频率、温度影响显著(如FR-4在1GHz时Dk=4.4,10GHz时降至3.8…

PCB阻抗控制的主要挑战

材料与工艺波动

基板介电常数(Dk)受频率、温度影响显著(如FR-4在1GHz时Dk=4.4,10GHz时降至3.8),导致阻抗漂移。

蚀刻公差(线宽±10%)、介质层厚度偏差(如±5μm)直接影响阻抗精度,需通过电镀补偿或高精度工艺控制。

设计复杂性

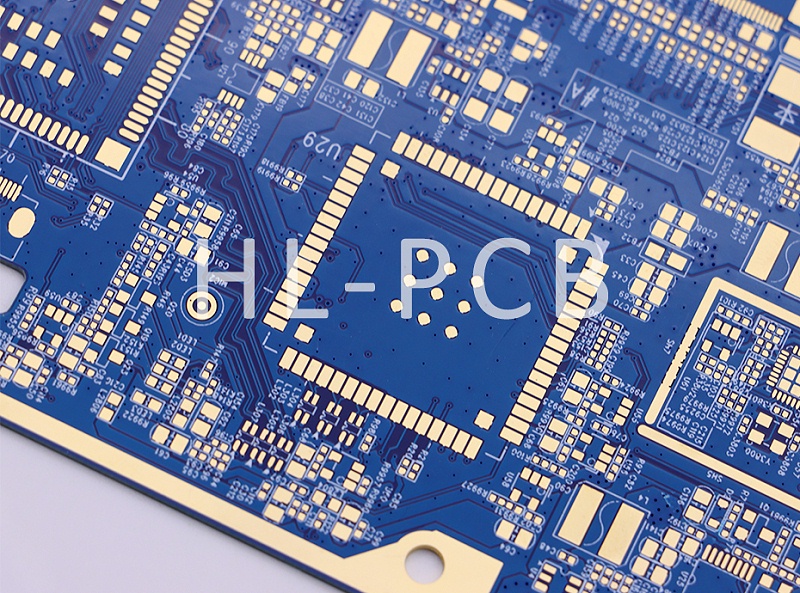

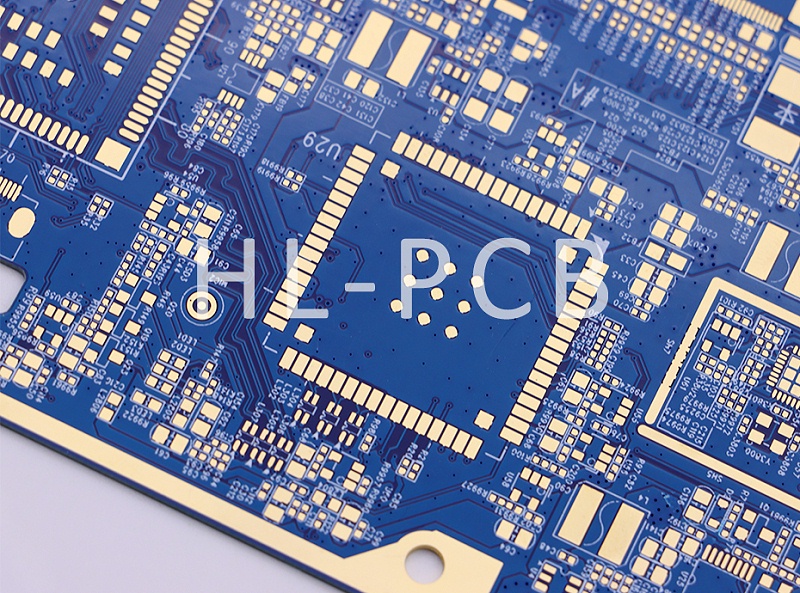

多层PCB中,信号层与参考平面的垂直距离变化(如微带线vs带状线)导致阻抗差异,需通过层叠优化(如对称结构)减少不连续性。

过孔寄生参数(如0.3mm过孔可能引入5-10Ω阻抗突变)需通过背钻或埋盲孔技术抑制。

高频信号干扰

差分线耦合效应使实际阻抗≠2×单端阻抗(如线距过小时阻抗可能低于90Ω),需通过仿真调整线宽/间距。

串扰与反射问题需通过3W规则(线间距≥3倍线宽)和阻抗匹配终端解决。

制造与验证难度

阻焊层覆盖使单端阻抗降低2Ω,需在设计阶段预补偿。

TDR测试受限于探头精度,需结合VNA和仿真工具闭环验证。

典型场景应对策略

高速接口(如USB4.0):采用低Dk材料(如Rogers 4350B),公差控制在±5%内。

射频电路:考虑趋肤效应,优化铜箔表面粗糙度以减少高频损耗。

通过材料选型、仿真优化与工艺协同,可系统性解决上述挑战。